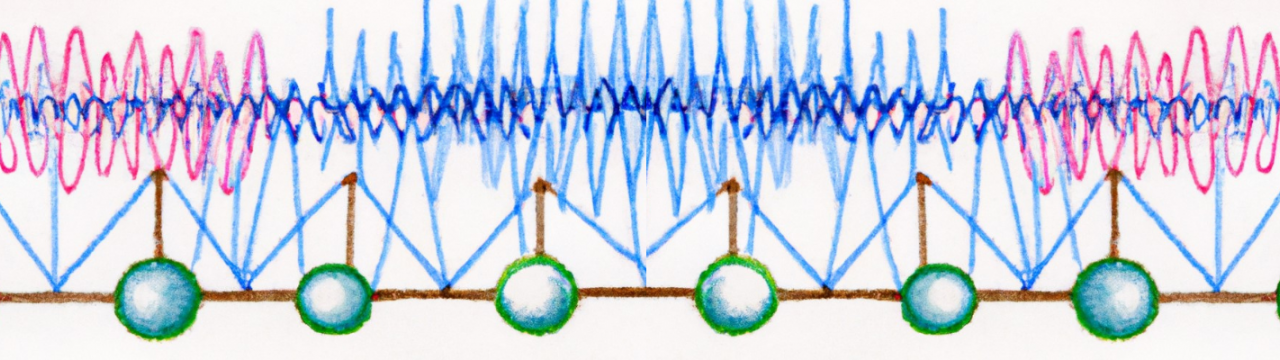

Kwantumtechnologie vereist vaak een groot aantal signalen om honderden of duizenden kwantumbits in een zeer koude cryostaat te besturen en te laten werken, terwijl de kwaliteit, tijd, schaalbaarheid en reproduceerbaarheid behouden blijven.

Dit knelpunt kan worden verholpen door input/output-componenten (bedrading, interfaces, connectoren, thermische klemmen, chipdragers) te optimaliseren om het R&D-proces te versnellen. Het zijn precies deze knelpunten die ons project beoogt te overwinnen.